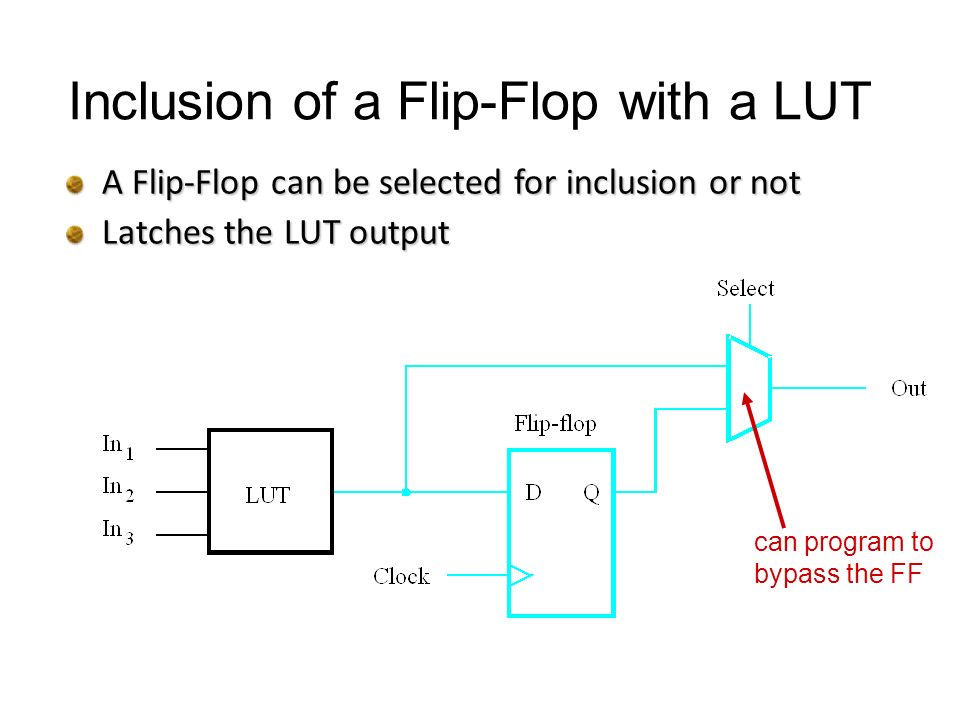

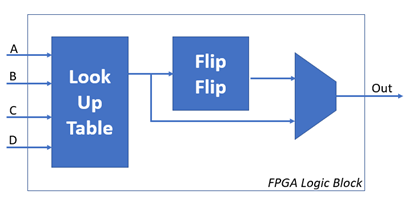

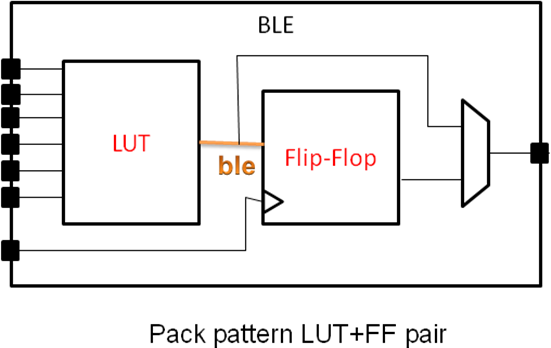

Figure .: A basic Logic Element (LE) with a K-input LUT, a flip-flop,... | Download Scientific Diagram

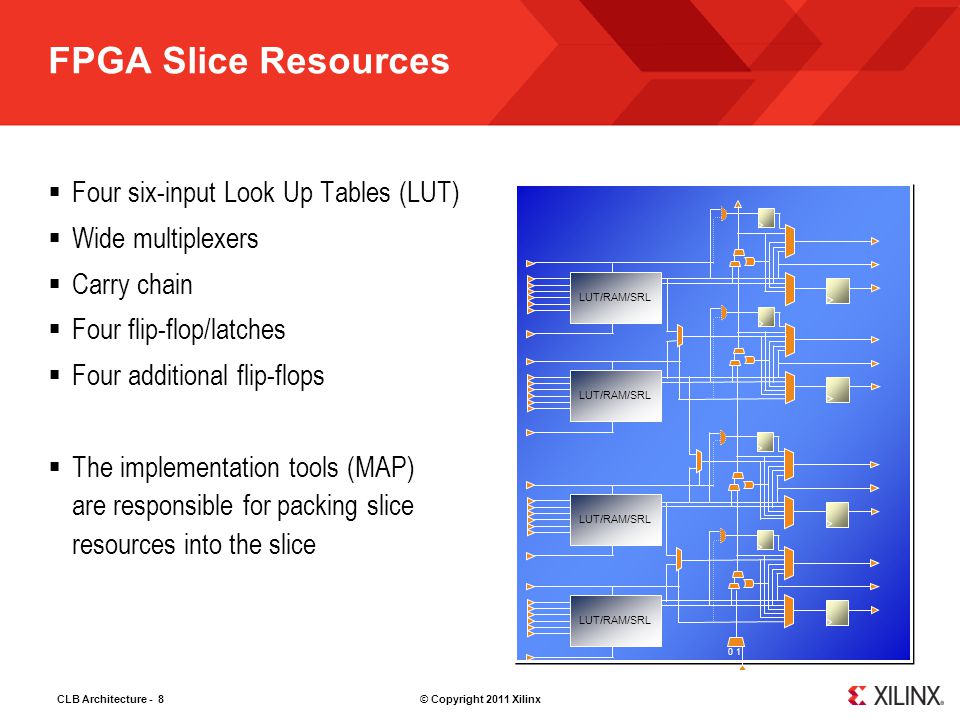

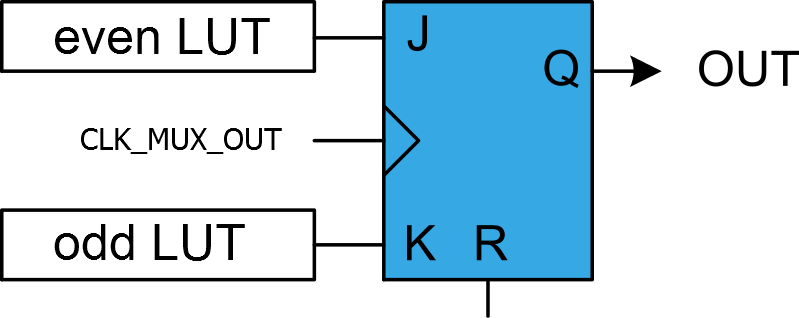

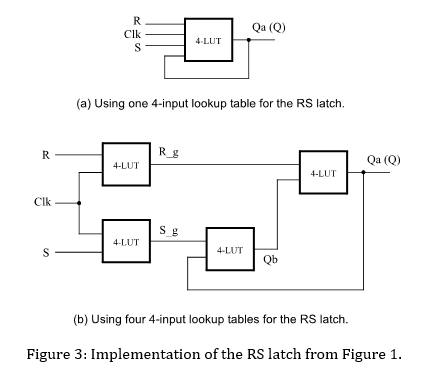

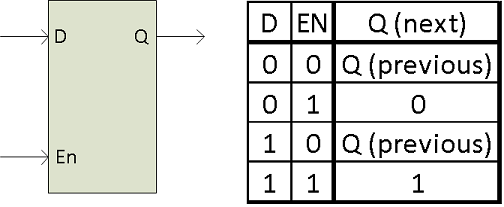

Introduction to FPGA Hardware Concepts (FPGA Module) - LabVIEW 2018 FPGA Module Help - National Instruments

62720 - Vivado Implementation - Placer reports higher LUTs utilization in "ERROR: [Place 30-380]" than what is seen in the post-opt utilization report